Datasheet microEnable 5 marathon deepVCL

i

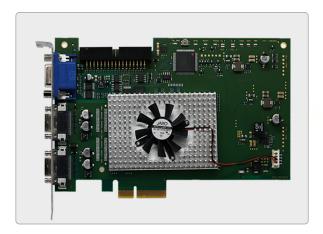

## microEnable 5 marathon deepVCL

### Product Profile of microEnable 5 marathon deepVCL

Scalable, intelligent image processing board for Deep Learning applications with image acquisition and processing by robust industrial MV standards

- Enables real-time image processing for Deep Learning

- Compliant to VisualApplets CNN operator

- Onboard image preprocessing functions

- Industrial multi-device, multi-camera support

- DMA 1800 / up to 1800 MB/s PCle Data bandwidth (PCle x4 Gen2)

- Supports opto-decoupled signals via front I/O

- Broad support of Third-party software interfaces

- Versatile application and industry usage

- Custom FPGA programming with VisualApplets supporting Xilinx Kintex FPGAs

- PoCL SafePower

## **Technical Description**

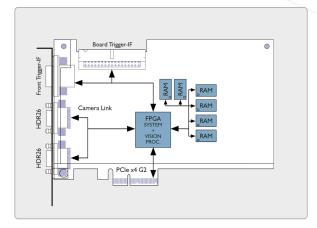

Programmable microEnable 5 marathon frame grabber with 2\* Camera Link ports (SDR26) for Base, DualBase, Medium and Full Configuration (incl. Deca/80bit mode), 2 GB DDR3RAM acquisition and image processing buffer, Xilinx Kintex 7 vision processor, PCle x4 (Gen 2) bus interface, DMA1800 technology. Prelicensed for VisualApplets (Base) and VisualApplets CNN applications. Documentation, SDK, supporting software tools, functional libraries with acquisition applets and drivers in delivery. Genuine compliance to VisualApplets FPGA programming environment.

| Article Details |                                    |

|-----------------|------------------------------------|

| Product Name    | microEnable 5 marathon deepVCL     |

| Match Code      | mE5-MA-deepVCL                     |

| Article No.     | 150636                             |

| Category        | V-Series (image acquisition board) |

| Device Features              |                                             |

|------------------------------|---------------------------------------------|

| Processor                    | Vision Processor                            |

| On Board Memory              | 2 GByte DDR3-RAM                            |

| Processor Board<br>Interface | n/a                                         |

| Data Forwarding              | n/a                                         |

| I/O Module Interfaces        | Trigger/GPIO-IF (Opto Trigger, TTL Trigger) |

| Camera Interface  | 9                                                                                |

|-------------------|----------------------------------------------------------------------------------|

| Standard          | Camera Link 2.0, up to 85 MHz Pixel Clock, extended cable length                 |

| Configurations    | CL-base, CL-dual base, CL-medium, CL-full, CL-deca (80bit)                       |

| Connectors        | 2* SDR26 (miniCL)                                                                |

| Cable Length      | extended length                                                                  |

| Power Output      | PoCL SafePower, 4W/12V per cable                                                 |

| Camera Support    | Area scan camera, line scan camera                                               |

| Sensor Type       | Grayscale sensor, CFA sensor (Bayer), RGB sensor                                 |

| Sensor Resolution | 64k*64k (area scan sensor, VisualApplets), 64k (line scan sensor, VisualApplets) |

| Bit Depth         | 8-16-bit (grayscale), 24-48-bit (color)                                          |

| Data Bandwidth    | 850 MB/s                                                                         |

| Test Environment  | Camera Simulator                                                                 |

| Controls and Ge                  | neral Purpose I/Os                                                                                                                                                                                                                                                                                                                                 |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Trigger Board GPIO<br>Interfaces | TTL Trigger board: 8 TTL in and 8 TTL out, max. input freq: 20 MHz; Opto Trigger boards (options): Up to 8 single-ended opto-coupled in (4,5V-28V) or 4 differential opto-coupled in (4,5-28V, RS422 compliant); 8 opto-coupled out (4,5V-28V), max. input freq: 2,5 MHz                                                                           |

| On-board GPIO<br>Interface       | 4 opto-coupled inputs (4,5 V -28 V), optional 2 opto-coupled differential inputs (RS422); 4 opto-coupled outputs (4,5 – 28 V); Shaft encoder input, programmable rescaler, multiple-camera synchronization                                                                                                                                         |

| On-board Front GPIO<br>Interface | 2 opto-coupled differential inputs (RS422) and 1 opto-coupled differential / single ended input; optional (conf.): 4 opto-coupled Inputs (4,5 V -28 V) with up to 1 MHz frequency□; 2 TTL outputs, up to 20 MHz frequency; shaft encoder input, programmable rescaler: multiple-camera synchronization; RS485 interface (PLC connection) scheduled |

| Synchronization and<br>Control   | Configurable Trigger System supporting several trigger modes (grabber controlled, external trigger, gated, software trigger) and shaft encoder functionality with backward compensation, Multi-Camera-Synchronization                                                                                                                              |

| GPIO Summary                     | onboard: 8in/8out (max.), TTL or opto-coupled; Front GPIO: up to 3 differential signals in, up to 4 single-ended signals in (depends on configuration), 2 TTL outputs                                                                                                                                                                              |

| Host PC Interface               |                                 |

|---------------------------------|---------------------------------|

| PC Bus Interface                | PCI Express x4 (Gen 2), DMA1800 |

| PC Bus Interface<br>Performance | up to 1.800 MB/s (sustainable)  |

| Physical and Environmental Information |                                                                                                                                          |  |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|--|

| Dimensions                             | PCIe Standard height, half length card: 167.64 mm length x 111.15 mm height                                                              |  |

| Approximate Weight                     | 165 g                                                                                                                                    |  |

| Power Consumption /<br>Power Source    | 12 V, 1.4 A (actual values depend on processing)                                                                                         |  |

| Operating<br>Temperature               | 50° (0 LFM*), 60° (100 LFM*) FPGA operating temperature: 0°C to 85°C, *LFM = Linear Feet per Minute, unit for measuring airflow velocity |  |

| Storage Temperature                    | '-50°C up to 80°C                                                                                                                        |  |

| Relative Humidity                      | 5%-90% non-condensing (operating), 0%-95% (storage)                                                                                      |  |

| MTBF                                   | pending                                                                                                                                  |  |

| Compliances                            | CE, RoHS, WEEE, REACH                                                                                                                    |  |

| Software                     |                                                                                                                                                                  |  |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Software Drivers             | Windows 10 $/$ 8 $/$ 7 (32-Bit), Windows 10 $/$ 8 $/$ 7 (64-Bit), Linux 32-Bit, Linux 64-Bit                                                                     |  |

| Software Tools               | microDisplay (Acquisition control and viewer), microDiagnostics (Service tool), GenlCam Explorer (Camera configuration tool), SDK, Documentation, Device Drivers |  |

| Software API                 | Silicon Software SDK, .net interface                                                                                                                             |  |

| FPGA Programming             | VisualApplets                                                                                                                                                    |  |

| BV Software<br>Compatibility | Common Vision Blox, Halcon, Cognex VisionPro, LabView, others on request                                                                                         |  |

## VisualApplets

Often, the goal of industrial image processing applications is to find 100% of all errors and to work in high resolution to identify even the smallest details, to acquire images in the shortest time possible, to detect defects and to forward the results. These tasks frequently require more computing power than a "standard system" can offer. There are solutions that begin the image processing right after the acquisition process but before the camera images are written to storage and taken over by the software.

The processors used in such solutions are designed for image processing. They process data with extremely high parallelism, thus guaranteeing the necessary data throughput. On all its frame grabbers, Silicon Software uses this FPGA technology. In the A-Series (frame grabbers with expanded image recording functions), we have already programmed important and valuable functions that can be activated via the configuration software. For V-Series models (programmable frame grabbers for individual image processing functions), we have released the FPGA for you, as our customer, for individual programming.

To ease your entry into hardware programming, we have developed software that enables you to graphically program FPGAs using data flow diagrams. This program is called VisualApplets.

VisualApplets makes it possible for you to write complex applications on your own, even after a short time, for the special processor. Even without hardware programming expertise. The program is geared toward both software programmers and application engineers. Program in the language of image processors without using hardware code. The simulation works with a rapid image output with which you can immediately check your algorithms and image processing steps.

We have built in many automatic correction functions and generators so that you can concentrate on your actual work. And should an error sneak in, you are immediately made aware of it in color, and solution approaches are offered to you.

An SDK output generates executable example code in C/C++, listing all the parameters (hardware register), in order to control the image processing application out of your software.

What does real time mean? By using FPGA technology, you have a deterministic relationship to the application that works after the start with a constant delay (latency) that is determined by the image processing algorithm. In most cases, this latency lies in the micrometer range.

## VisualApplets (ctd.)

VisualApplets simplifies image processing programming for you. You can fall back on libraries with over 200 operators. You can create your own libraries for commonly used image processing steps or import them from available hardware code (EDIF over VHDL/Verilog).

With VisualApplets, you acquire a powerful tool that offers you new ways forward for your system solution.

VisualApplets is available for Silicon Software V-Series frame grabbers, including VisualApplets-compatible cameras and imaging devices.

V-Series frame grabbers are already pre-licensed for use with VisualApplets in the basic version. VisualApplets offers several versions of its programming environment; additionally, you can license further operator libraries to expand the range of functions.

In 2006, VisualApplets was honored with the international Vision Award. It has been successfully used in the most diverse industrial applications, both using frame grabbers and in VisualApplets-compatible industrial cameras and image processing devices.

# Technical Setup

### Board/Housing Measurement

Height: 111,15 mm Length: 167.64 mm Width: no width Mounting: PCle slot

Screw Mounting: no screw mounting Protecion Class: no class defined Material: PCB, RoHS compliant

Screws: no screws

### PRODUCT VARIATIONS

LightBridge ACL LightBridge VCL microEnable 5 marathon ACL microEnable 5 marathon VCL microEnable 5 marathon VCLx

### PRODUCT EXTENSIONS

Opto-coupled Trigger Board – mE5, Match Code: TRG-

OPTO5, Art.No.: 155010

TTL Trigger Board - mE4. Match Code: TRG-TTL4, Art

No.: 101251

### ORDERING INFO

microEnable 5 marathon deepVCL, mE5-MA-deepVCL, Art No.: 150636

Copyright © Silicon Software, 2019 Generated on 11. March 2019

Silicon Software GmbH Konrad-Zuse-Ring 28 68163 Mannheim Germany [t] +49.621.798507-0

[f] +49.621.798507-10

[e] info@silicon.software

[w] https://silicon.software

Silicon Software Inc 1 Tara Boulevard, Suite 200 Nashua, NH 03062 USA [t] +1.888.808 3670

[f] +1.888.808 3670

[e] americas@silicon.software

[w] https://silicon.software

Silicon Software Americas Inc 3055 St-Martin Blvd., Suite 500 Laval, Qc., H7T0J3 Canada [t] +1.888.808 3670

[f] +1.888.808 3670

[e] americas@silicon.software

[w] https://silicon.software

We reserve the right of technical modifications, changes of the equipment features and adaptations to current specification. Typing and setting mistakes and other errors cannot be excluded and are therefore also reserved. In recent publications availability, also by technical generation, previous cease to be valid.